Index

Related

- Latch

- Circuiti sequenziali

- Digitali (class)]]

Definizione

Il Gated Latch è un circuito sequenziale ed sincrono utilizzato per la memorizzazione di un bit

Ho un funzionamento identico al Latch SR ma è presente un input supplementare, ovvero un segnale di controllo che permette il cambio dei valori in ingresso solo per tempi discreti predefiniti.

Spesso viene utilizzato un segnale di clock come segnale di abilitazione, essendo un segnale periodico permette la sincronizzazione di più componenti sincrone

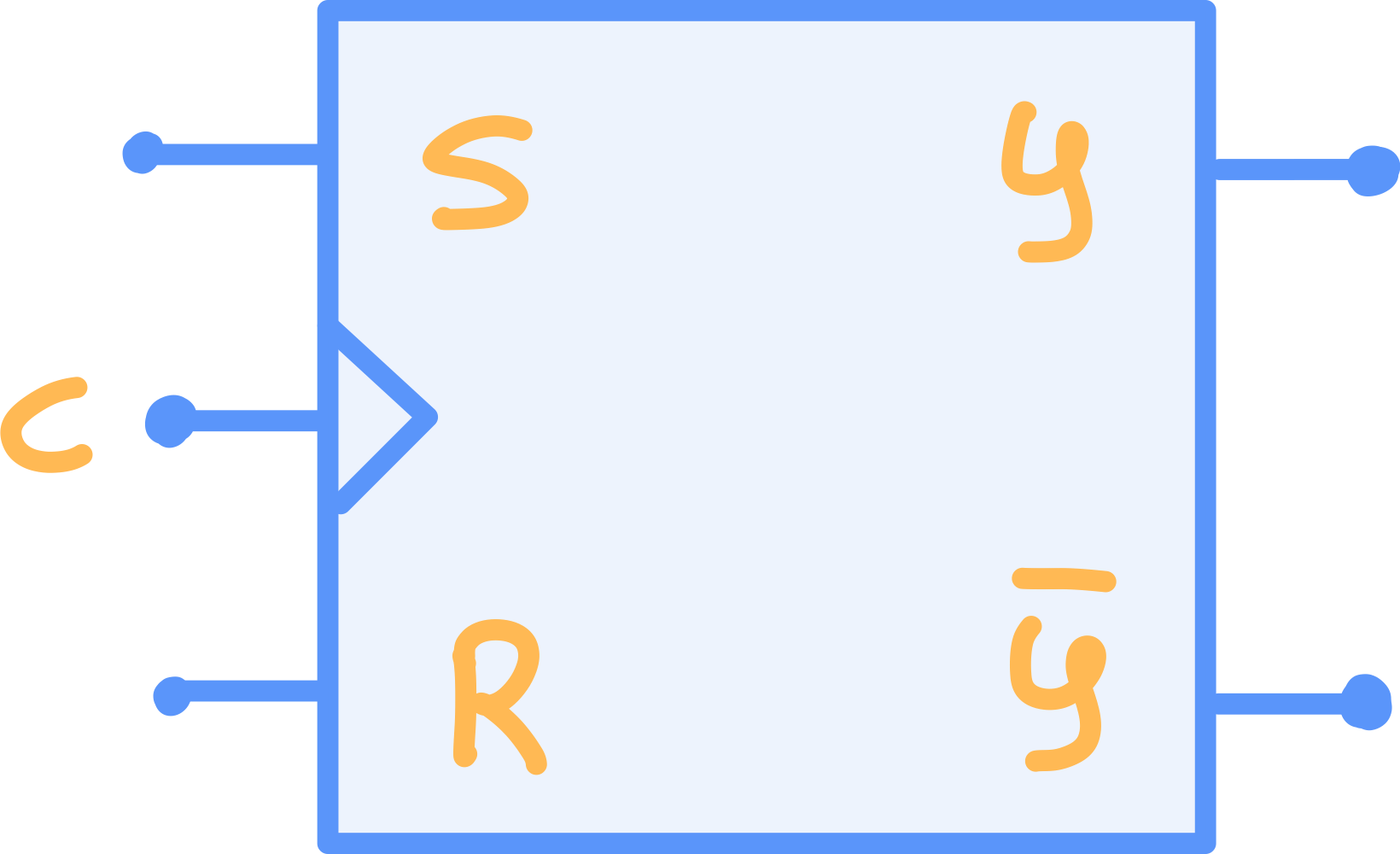

Simbolo

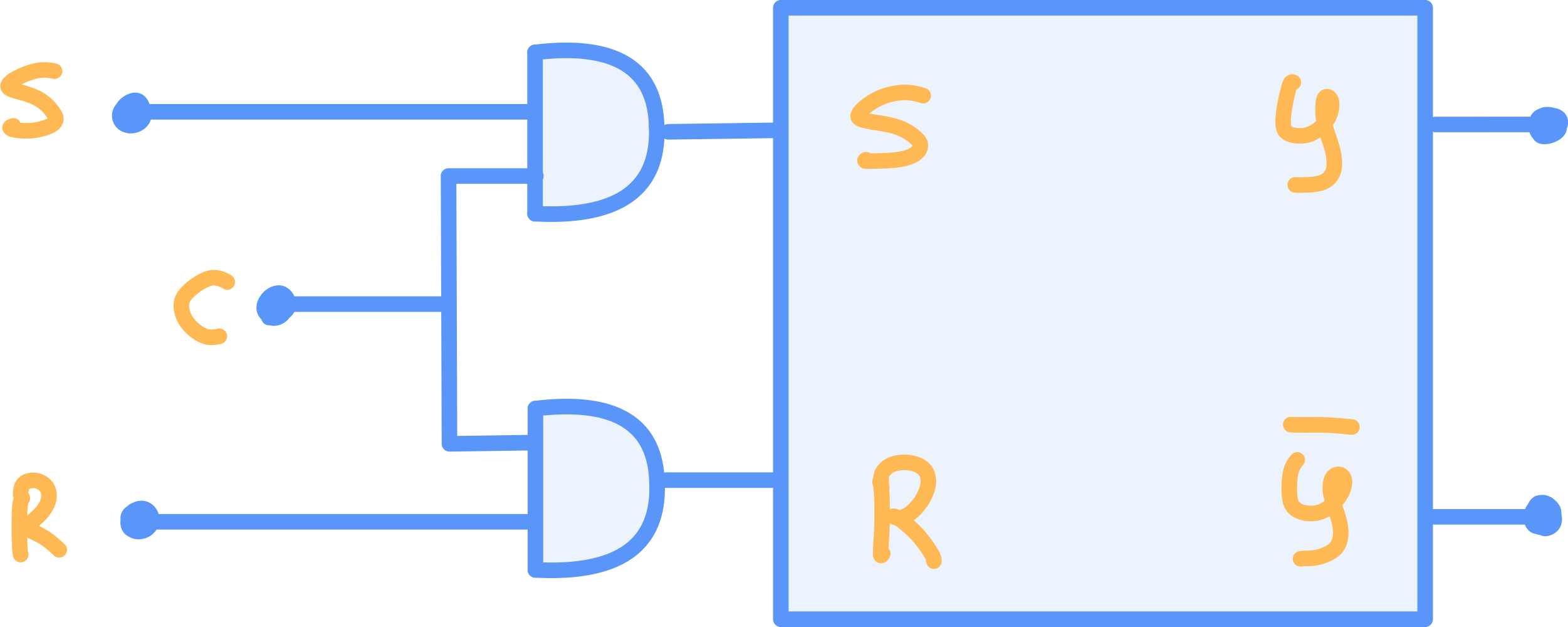

Rappresentazione circuitale AND

I/O

Input:

- s = Set

- r = Reset

Output:

- y = Stato del latch (output)

Circuito + Funzionamento

Circuito

Funzionamento

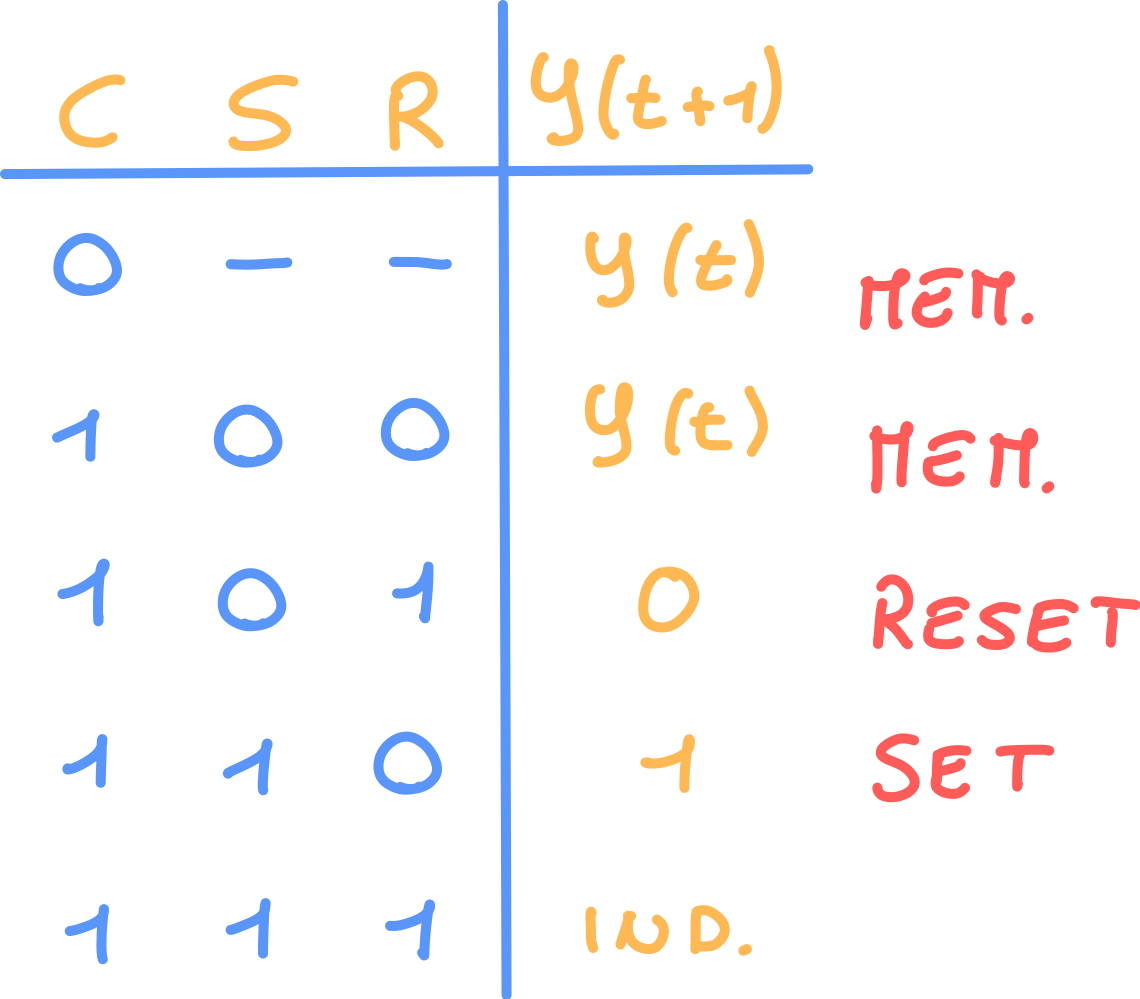

Se C = 0 ⇒ Memorizzazione indipendente dai valori di S e R Se C = 1:

- Stato di Set: quando S = 1 ⇒ y = 1

- Stato di Reset: quando R = 1 ⇒ y = 0

- Stato di Memorizzazione: quando S = 0 e R = 0 ⇒ y rimane invariato

- Stato Indefinito: quando S = 1 e Y = 1 ⇒ comportamento anomalo in cui entrambe le uscite sono uguali a 0

oss: se c = 1 si comporta com Latch SR normale

Tabella stati futuri

oss:

- y(t) ⇒ stato presente

- y(t+1) ⇒ stato futuro

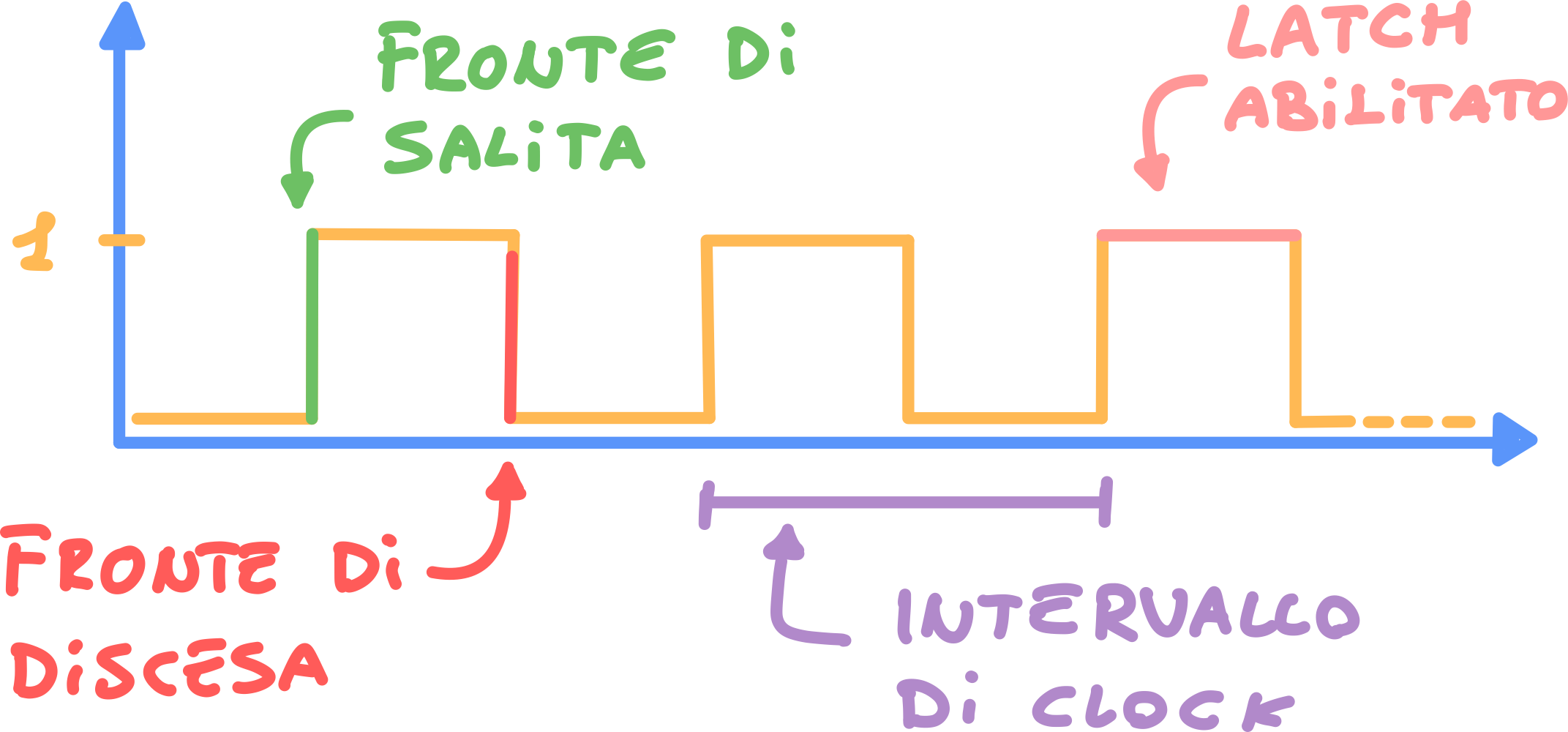

Diagramma temporale

oss: latch è abilitato per tutto il periodo in cui il clock vale 1