Index

Related

Definizione

- Il Latch SR (latch set and reset) è un circuito sequenziale, asincrono base utilizzato per la memorizzazione di un bit.

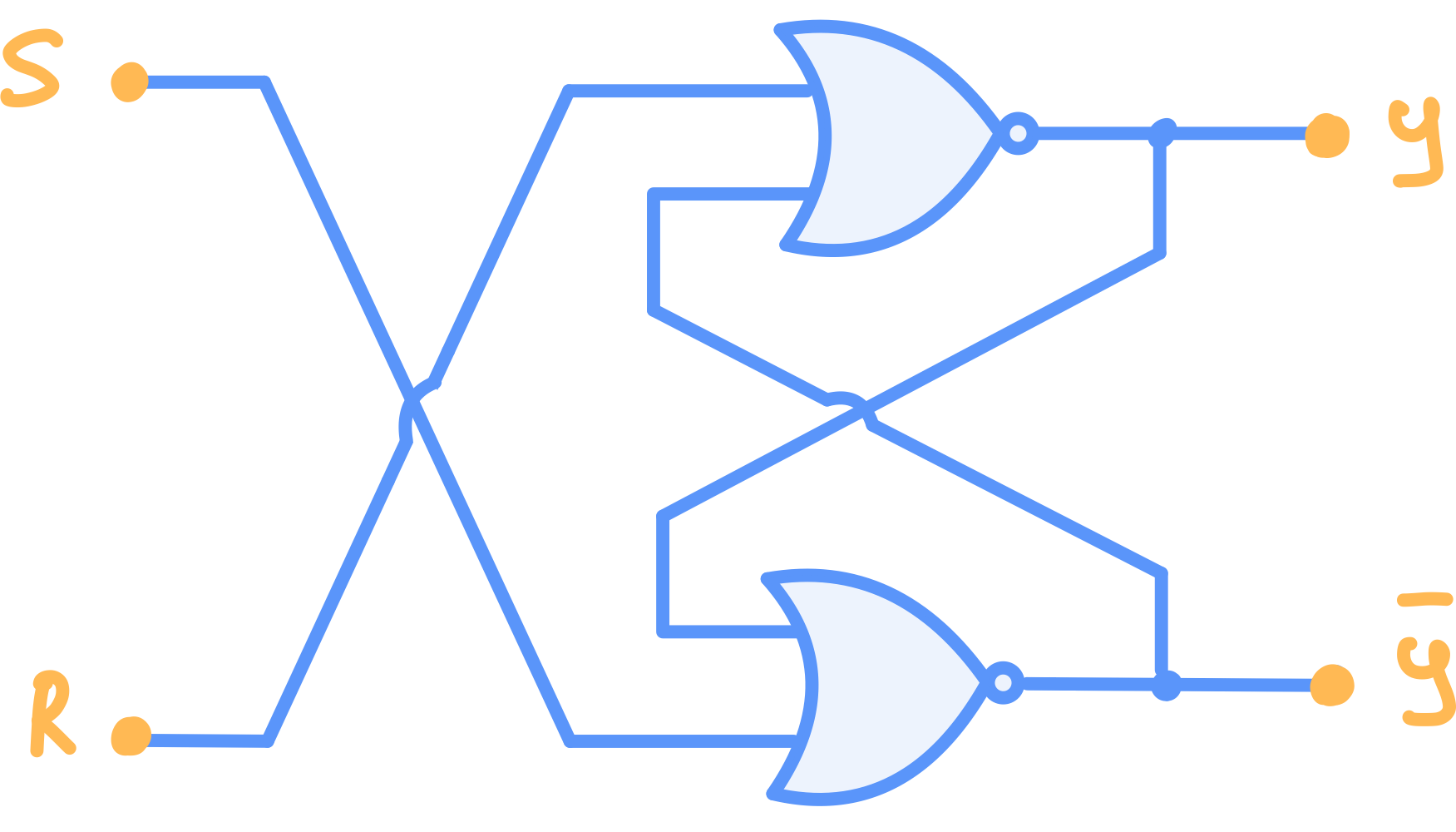

- È il tipo di lath più semplice, costruito a partire da due porte nor con collegamenti incrociati

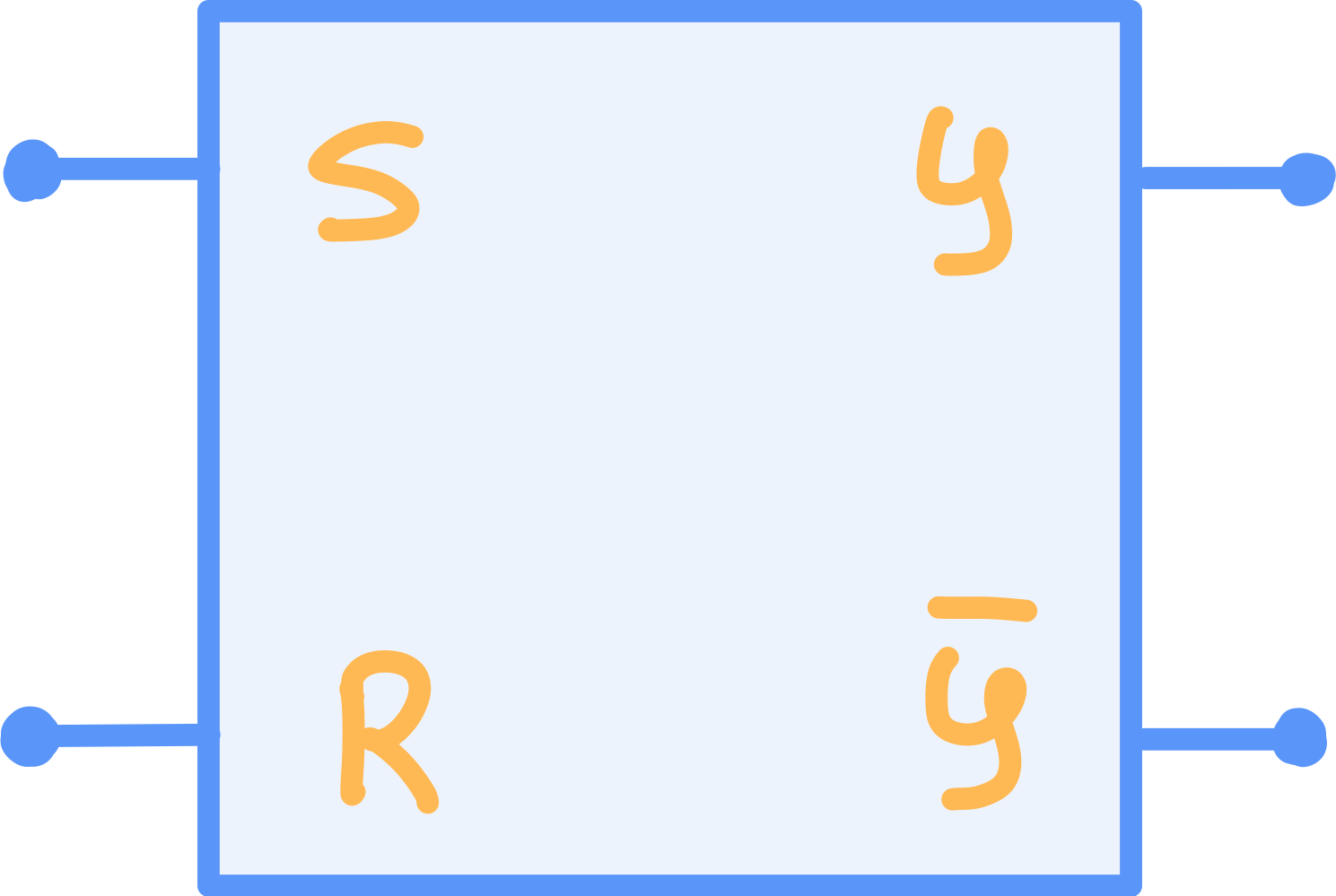

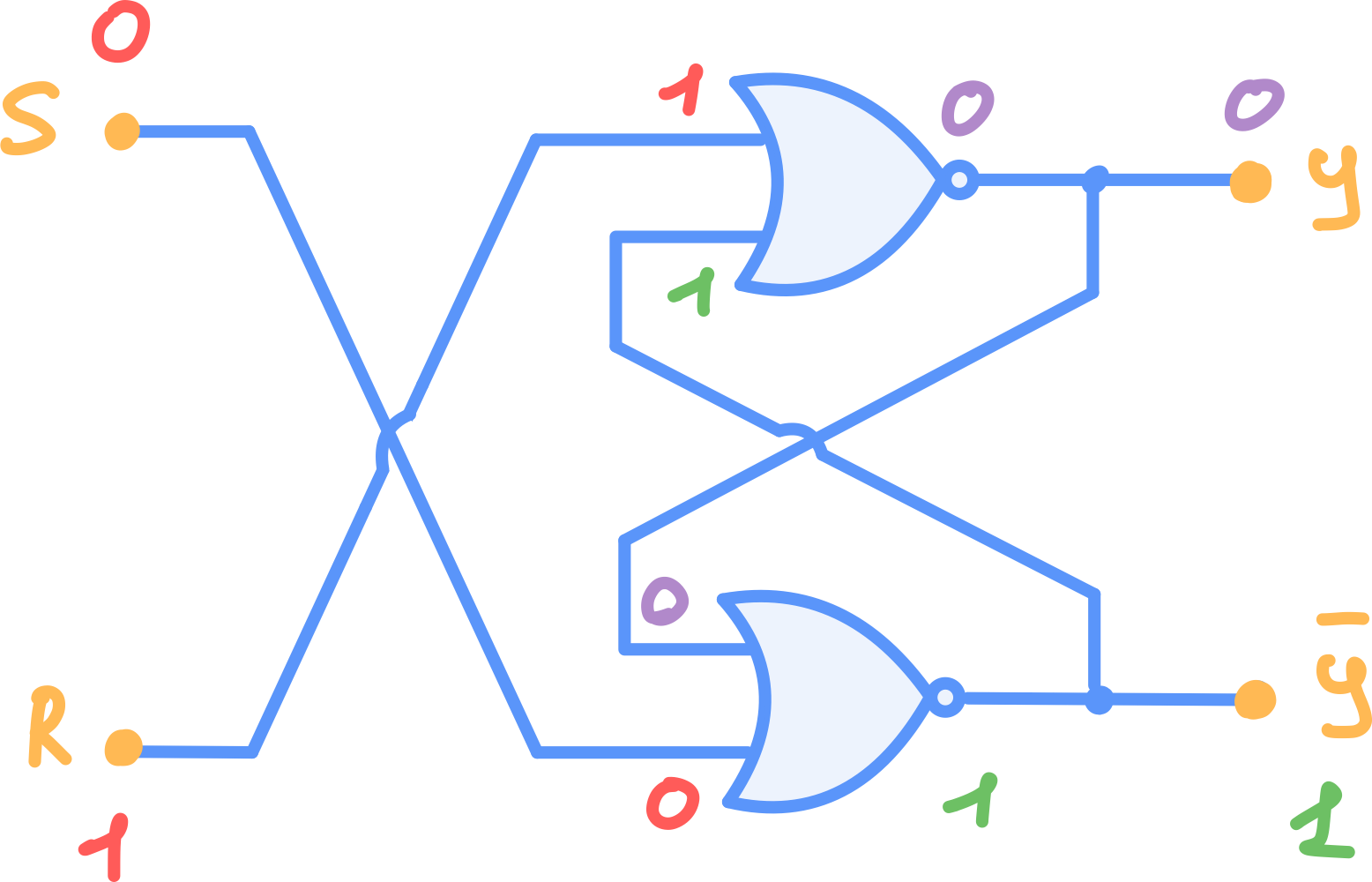

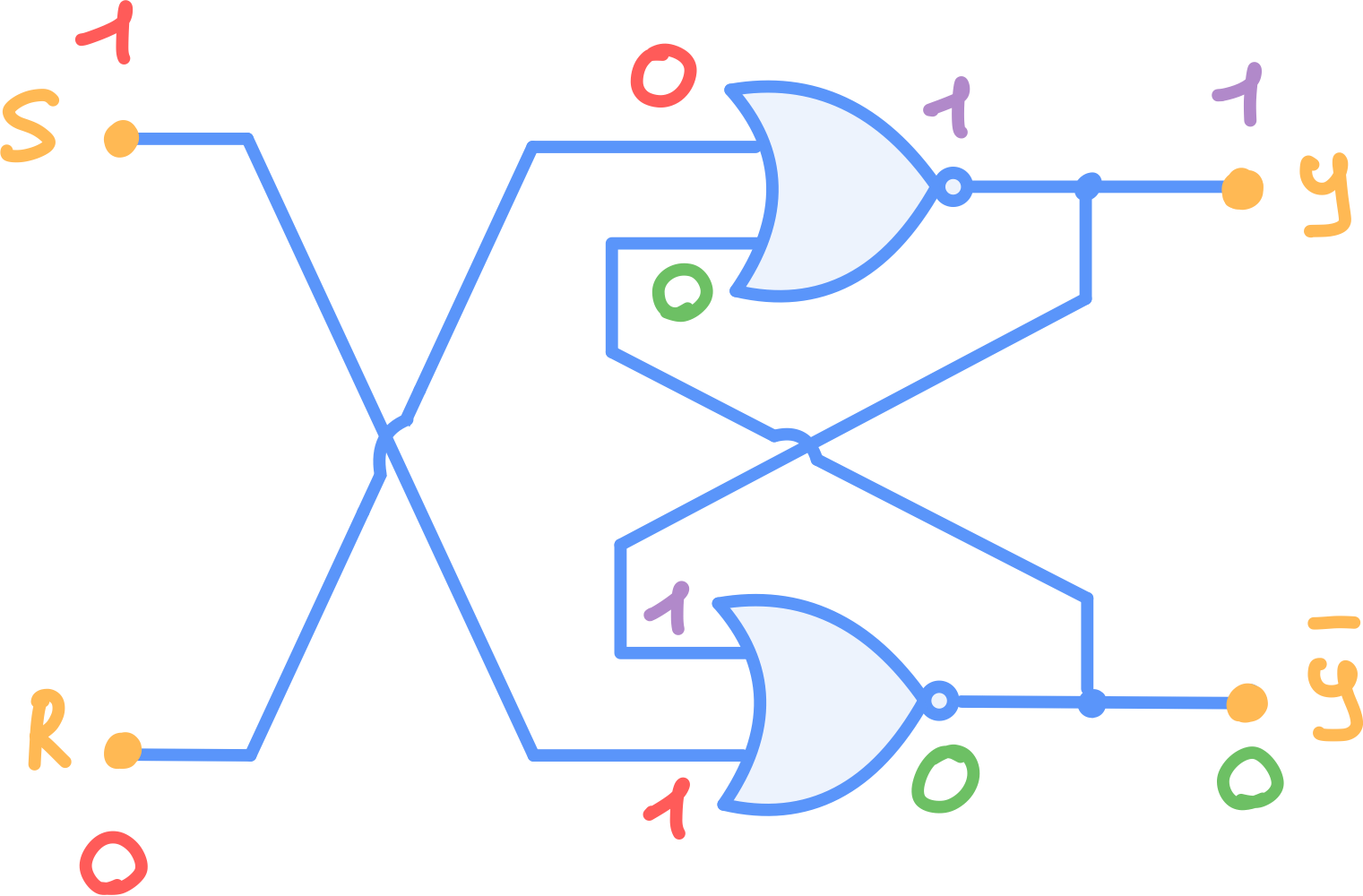

Rappresentazione circuitale

I/O

Input:

- s = Set

- r = Reset

Output:

- y = Stato del latch (output)

Circuito + Funzionamento

Circuito

Funzionamento

- Stato di Set: quando S = 1 ⇒ y = 1

- Stato di Reset: quando R = 1 ⇒ y = 0

- Stato di Memorizzazione: quando S = 0 e R = 0 ⇒ y rimane invariato

- Stato Indefinito: quando S = 1 e Y = 1 ⇒ comportamento anomalo in cui entrambe le uscite sono uguali a 0

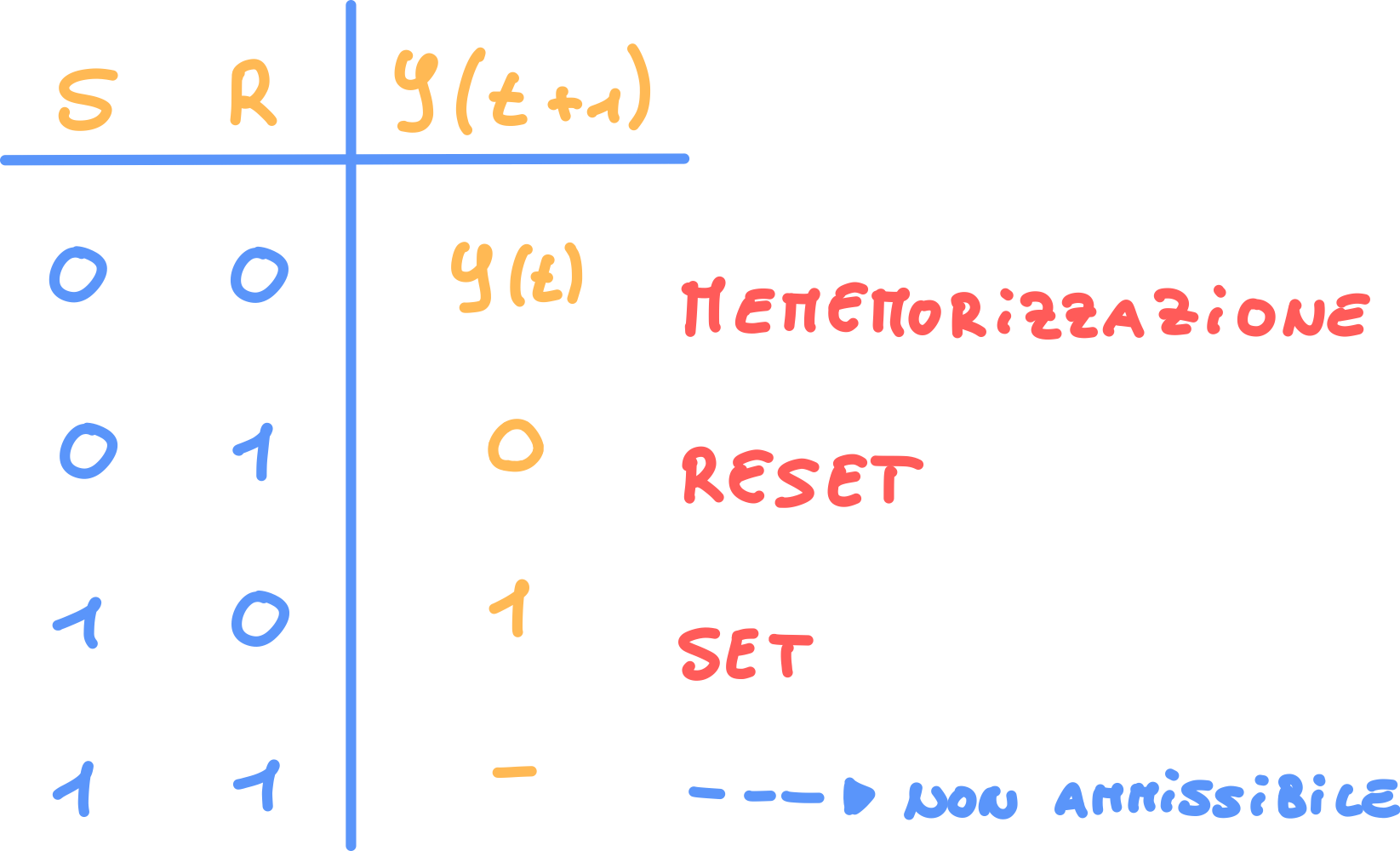

Tabella stati futuri

oss:

- y(t) ⇒ stato presente

- y(t+1) ⇒ stato futuro

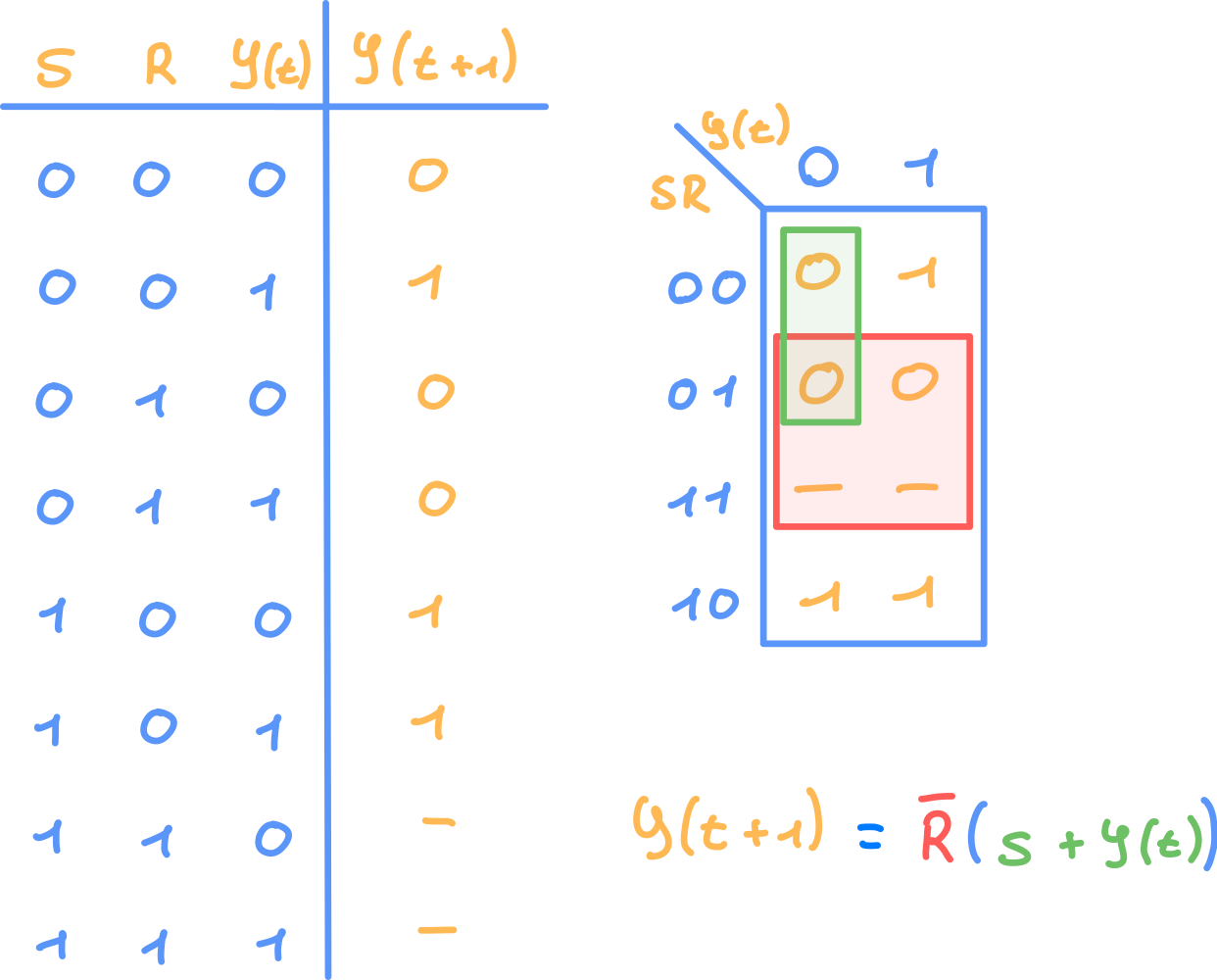

Formula

Formula

- y = y(t)

- Y = y(t+1)

Come ricavare formula

Come vuole Prof

- Funziona perché non è ammesso r = 1 e s = 1

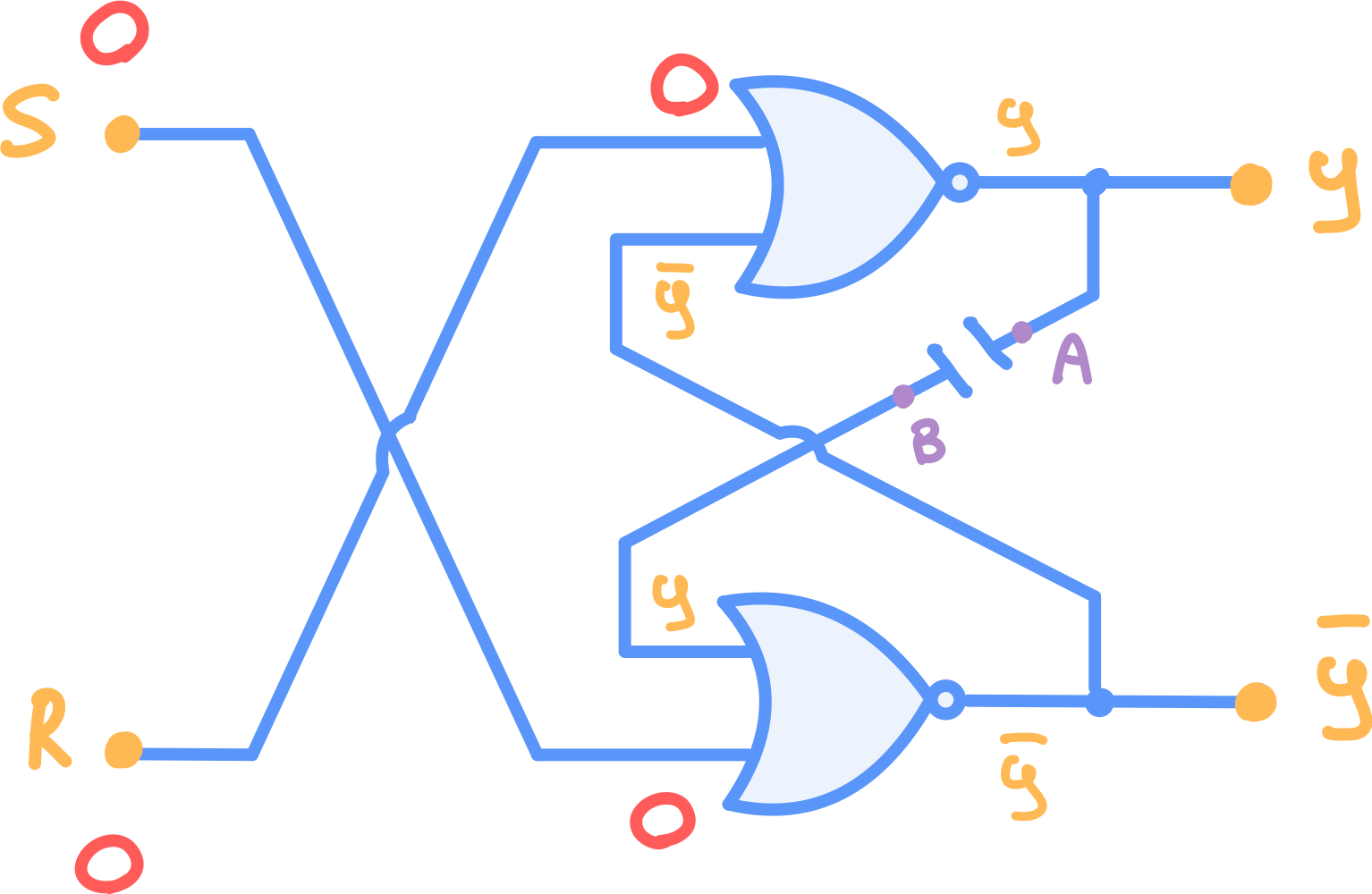

Studio degli stati

Set

Reset

Memorizzazione>

Per dimostrare che il latch mantiene lo stato precedente “tagliamo” il filo che collega l’uscita y all’entrata della porta NOR. Otteniamo così due punti (A e B). Se, partendo dal punto B, arriviamo al punto A con valore invariato, allora il latch ha mantenuto lo stato precedente.